#### NATIONAL INSTRUMENTS™ ALLIANCE PARTNER OF 2015/2016 WINNER OF THE NATIONAL INSTRUMENTS™ TECHNICAL INNOVATION AWARD | WINNER OF THE WIR TECHNICAL INNOVATION AWARD!

## Overview

- 1. LV 124: covers tests for electric and electronic components for use in motor vehicles up to 3,5 t with a <u>12 V</u> electric system

- 2. LV 148: covers tests for electric and electronic components in motor vehicles <u>48V</u> electrical system

- 3. LV 124 vs. LV 148

- 4. WKS Informatik solutions for electrical tests

References

- Volkswagen 80000 Electric and Electronic Components in Motor Vehicles up to 3,5 t General Requirements, Test Conditions and Tests Issue June 2013

- VDA 320 Elektrische und elektronische Komponenten im Kraftfahrzeug 48V-Bordnetz Anforderungen und Prüfungen Issue August 2014

## LV 124

| Voltages and currents |                                              |  |  |

|-----------------------|----------------------------------------------|--|--|

| VN                    | Nominal voltage                              |  |  |

| VBmin                 | Lower operating voltage limit                |  |  |

| VB                    | Operating voltage                            |  |  |

| VBmax                 | Upper operating voltage limit                |  |  |

| Vmax                  | Maximum voltage that may occur during a test |  |  |

| Vmin                  | Minimum voltage that may occur during a test |  |  |

| VPP                   | Peak-peak voltage                            |  |  |

| Veff                  | RMS value of a voltage                       |  |  |

| Vtest                 | Test voltage                                 |  |  |

| IN                    | Nominal current                              |  |  |

| GND                   | Device ground                                |  |  |

| VA, VT, VS, VR        | Voltage level of the start voltage pulse     |  |  |

### Times/durations

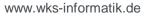

tr Rise time (e.g., of a voltage curve)

tf Fall time (e.g., of a voltage curve)

| Temperatures |                               |  |  |

|--------------|-------------------------------|--|--|

| Tmin         | Minimum operating temperature |  |  |

| TRT          | Room temperature              |  |  |

| Tmax         | Maximum operating temperature |  |  |

| Ttest        | Test temperature              |  |  |

| Encoding | V <sub>Bmin</sub> | V <sub>Bmax</sub> | Description                                                |

|----------|-------------------|-------------------|------------------------------------------------------------|

| а        | 6 V               | 16 V              | For functions that must retain their performance during    |

|          |                   |                   | starting of the engine                                     |

| b        | 8 V               | 16 V              | For functions that do not have to retain their performance |

|          |                   |                   | during starting of the engine                              |

|          |                   |                   |                                                            |

|          |                   |                   | This encoding must only be used if the component cannot    |

|          |                   |                   | be classified in the encoding a, c or d.                   |

| С        | 9 V               | 16 V              | For functions that must retain their performance           |

|          |                   |                   | when the engine is not running                             |

| d 、      | 9,8 V             | 16 V              | For functions that must retain their performance           |

| 1 AV     |                   |                   | when the engine is running                                 |

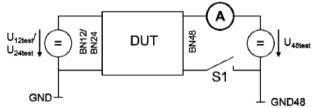

## LV 148

ttest

| Terms                     |                                       |

|---------------------------|---------------------------------------|

| A, B, C, D in<br>Diagrams | Functional status A, B, C, D          |

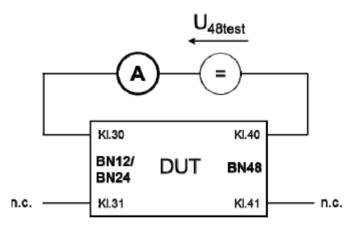

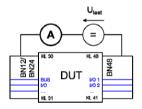

| BN12                      | 12V-on board supply                   |

| BN24                      | 24V-on board supply                   |

| BN48                      | 48V-on board supply                   |

| GND                       | Ground – Masse BN12/BN24 (Kl. 31)     |

| GND48                     | Ground 48 V – Masse BN48 (Kl. 41)     |

| n.c.                      | Not connected                         |

| РТВ                       | Physikalisch-Technische Bundesanstalt |

| RMS                       | Root Mean Square                      |

#### **Times/durations**

| tr | Rise time (e.g., of a voltage curve) |

|----|--------------------------------------|

| tf | Fall time (e.g., of a voltage curve) |

| Fall | time | (e.g., | OT | а | voltage | curve |

|------|------|--------|----|---|---------|-------|

|      |      |        |    |   |         |       |

Test time

#### Temperatures

| =     |                               |

|-------|-------------------------------|

| Tmin  | Minimum operating temperature |

| TRT   | Room temperature              |

| Tmax  | Maximum operating temperature |

| Ttest | Test temperature              |

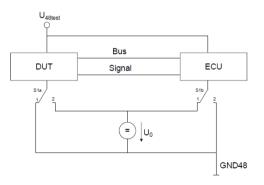

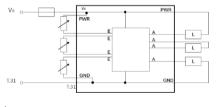

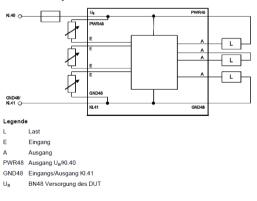

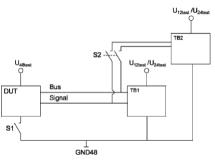

- Klemme 40 is the Plus of the 48 V supply.

- · Klemme 41 is the Ground of the 48 V supply.

WKS

Informatik Experts in Testing

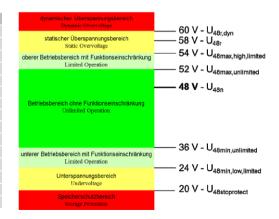

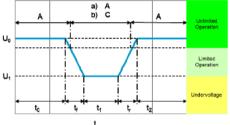

| Shortcut            | Terms LV 148                                                              | Value |

|---------------------|---------------------------------------------------------------------------|-------|

| U48r,dyn            | Lower voltage limit of the dynamic overvoltage range                      | 60 V  |

| U48r                | Lower voltage limit of the 2 V tolerance to the dynamic overvoltage range | 58 V  |

| U48max,high,limited | Max. voltage of the upper operating range with functional restriction     | 54 V  |

| U48max,unlimited    | Max. voltage of the operating range without functional restriction        | 52 V  |

| U48n                | BN48- nominal voltage                                                     | 48 V  |

| U48min,unlimited    | Min. voltage of the operating range without functional restriction        | 36 V  |

| U48min,low,limited  | Min. voltage of the lower operating range with functional restriction     | 24 V  |

| U48stoprotect       | Accumulator protected voltage                                             | 20 V  |

| U48pp               | Peak – peak- voltage                                                      |       |

| U48rms              | Effektive value of a voltage                                              |       |

| U48max              | Maximum voltage that may occur during a test                              |       |

| U48min              | Minimum voltage that may occur during a test                              |       |

| U48test             | BN48- test voltage                                                        |       |

| U12test             | BN12- test voltage                                                        | 14 V  |

| U24test             | BN24- test voltage                                                        | 28 V  |

| LV 124 | LV | 148 |

|--------|----|-----|

|--------|----|-----|

| Frequencies     | ±1%     | ±1%     |

|-----------------|---------|---------|

| Temperatures    | ±2 °C   | ±2 °C   |

| Humidity        | ±5%     | ±5%     |

| Times/durations | +5%; 0% | +5%; 0% |

| Voltages        | ±2%     | ±0.5%   |

| Currents        | ±2%     | ±2%     |

| Room<br>temperature                | TRT = 23 °C ± 5 °C                               | TRT = 23 °C ± 5 °C                                 |  |

|------------------------------------|--------------------------------------------------|----------------------------------------------------|--|

| Humidity                           | Hrel = 25% to 75% relative humidity              | 25 % (+ 5 % bis 0 %)<br>to<br>75 % (- 5 % bis 0 %) |  |

| Test<br>temperature                | Ttest = TRT                                      | Ttest = TRT                                        |  |

| Operating<br>voltage<br>(for test) | VB = 14 V                                        | U48max                                             |  |

| Source<br>impedance Ri             | Ri ≤ 100 mΩ (E6)<br>Ri < 30 mΩ / 100 mΩ<br>(E15) | 10 mOhm ≤ Ri ≤ 100<br>mOhm                         |  |

## Tolerances & standard values

## LV 124

#### **Functional status A**

The DUT must fulfill all functions during and after exposure to the test parameters. Functional status  ${\bf B}$

The DUT must fulfill all functions during exposure to the test parameters; however, one or more functions can lie outside the specified tolerance. After exposure to the test parameters, the DUT must automatically achieve functional status A again.

#### **Functional status C**

The DUT does not fulfill one or more functions during exposure to the test parameters. After exposure to the test parameters, the DUT must automatically achieve functional status A again. Undefined functions are not permissible at any time.

#### **Functional status D**

The DUT does not fulfill one or more functions during exposure to the test parameters. After exposure to the test parameters, the DUT must achieve functional status A again by means of a terminal changeover, a reset, or a simple intervention (e.g., replacement of a defective fuse). Undefined functions are not permissible at any time.

#### **Functional status E**

The DUT does not fulfill one or more functions during exposure to the test parameters and must be repaired or replaced after exposure to the test parameters.

The device under test (DUT) must comply with the requirements for nonflammability as per UL94-v0.

## LV 148

#### Functional status A

The DUT must fulfill all functions during and after exposure to the test parameters. Functional status  ${\bf B}$

The DUT must fulfill all functions during exposure to the test parameters; however, one or more functions can lie outside the specified tolerance. After exposure to the test parameters, the DUT must automatically achieve functional status A again.

#### **Functional status C**

The DUT does not fulfill one or more functions during exposure to the test parameters. After exposure to the test parameters, the DUT must automatically achieve functional status A or B again. Undefined functions are not permissible at any time.

#### Functional status D

The DUT does not fulfill one or more functions during exposure to the test parameters. After exposure to the test parameters, the DUT must achieve functional status A again by means of a terminal changeover, a reset, or a simple intervention (e.g., replacement of a defective fuse). Undefined functions are not permissible at any time.

#### **Functional status E**

The DUT does not fulfill one or more functions during exposure to the test parameters and must be repaired or replaced after exposure to the test parameters. The device under test (DUT) must comply with the requirements for nonflammability as

The device under test (DUT) must comply with the requirements for nonflammability as per UL94-v0.

An electrical test begins when the DUT is completely started up and is in functional status A.

A set of sensitive parameters, so-called key parameters, e.g. closed-circuit current consumption, operating currents, output voltages, contact resistances, input impedances, signal rates (rise/fall times), and bus specifications, must be defined in the Component Performance Specification or in agreement with the purchaser. The key parameters to be monitored must be recorded during each test.

Before and after each test, the DUTs must be subjected to a **parameter test (small):** The key parameters must be measured and the functional behavior of the components must be examined at TRT and VB

Before the first and after the last electrical test, the **parameter test (large):** The key parameters must be measured and the functional behavior of the components must be measured at temperatures Tmax, TRT, and Tmin, in each case at voltages VBmin, VB, and VBmax.

Before and after each test, the DUTs must be subjected to a **parameter test (small)**: The key parameters must be measured and the functional behavior of the components must be examined at TRT and U48n.

#### **Operating mode I - DUT not electrically connected**

#### **Operating mode I.a**

The DUT is not electrically connected, without plug and harness. Any present coolant circuit is not filled, and the connections are sealed.

#### **Operating mode I.b**

The DUT is not electrically connected, but with connected plugs and harness. Any present coolant circuit is filled, and the coolant hoses are connected.

#### **Operating mode II - DUT electrically connected**

#### **Operating mode II.a**

The DUT must be operated without operating load. Any present coolant circuit must be filled, and the coolant hoses must be connected. If necessary, the flow rate and temperature of the cooling medium must be set – as specified in the Component Performance Specification.

#### **Operating mode II.b**

The DUT must be operated with minimal operating load. The DUT must be operated in a way that minimal self-heating occurs (e.g., by reducing a continuous output power or by infrequent activation of external loads). Any present coolant circuit must be filled, and the coolant hoses must be connected. If necessary, the flow rate and temperature of the cooling medium must be set – as specified in the Component Performance Specification.

#### **Operating mode II.c**

The DUT must be operated at maximum load (power user, but no misuse). The DUT must be operated in a way that maximum self-heating occurs (e.g., by means of a realistic maximization of a continuous output performance or frequent activation of external loads).

Any present coolant circuit must be filled, and the coolant hoses must be connected. If necessary, the flow rate and temperature of the cooling medium must be set – as specified in the Component Performance Specification.

| E-01 Long-term overvoltage                               | Components supplied via the 12 V electric system                                            | E48-01a,b Long-term overvoltage                              |  |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|

| E-02 Transient overvoltage                               | Components supplied via the 12 V electric system                                            | E48-02 Transient overvoltage                                 |  |

| E-03 Transient undervoltage                              | Components supplied via the 12 V electric system                                            | E48-03 Transient undervoltage                                |  |

| E-04 Jump start                                          | Components supplied via the 12 V electric system                                            | E48-04 Jump start                                            |  |

| E-05 Load dump                                           | Components supplied via the 12 V electric system                                            | E48-05 Superimposed alternating voltage                      |  |

| E-06 Superimposed alternating voltage                    | Components supplied via the 12 V electric system                                            | E48-06a,b,c Slow decrease and increase of the supply voltage |  |

| E-07 Slow decrease and increase of the supply voltage    | All components                                                                              | E48-07 Slow decrease, quick increase of the supply voltage   |  |

| E-08 Slow decrease, quick increase of the supply voltage | All components                                                                              | E48-08 Reset behavior                                        |  |

| E-09 Reset behavior                                      | All components                                                                              | E48-9 Short interruptions                                    |  |

| E-10 Short interruptions                                 | All components                                                                              | E48-10 Start pulses                                          |  |

| E-11 Start pulses                                        | Components supplied via the 12 V electric system                                            | E48-11 Masseverlust BN48                                     |  |

| E-12 Voltage curve with electric system control          | Components supplied via the 12 V electric system                                            | E48-12 Ground offset                                         |  |

| E-13 Pin interruption                                    | All components                                                                              | E48-13 Internal dielectric strength                          |  |

| E-14 Connector interruption                              | All components                                                                              | E48-14 Closed-circuit current                                |  |

| E-15 Reverse polarity                                    | Components that can be subjected to reverse polarity in the vehicle                         | E48-15 Operation in range without function limitation        |  |

| E-16 Ground offset                                       | All components                                                                              | E48-16 Operation in the upper range with function limitation |  |

| E-17 Short circuit in signal circuit and load circuits   | All components                                                                              | E48-17 Operation in the lower range with function limitation |  |

| E-18 Insulation resistance                               | Components with galvanically isolated portions                                              | E48-18 Overvoltage range                                     |  |

| E-19 Closed-circuit current                              | Components that are continuously supplied with voltage                                      | E48-19 Undervoltage range                                    |  |

| E-20 Dielectric strength                                 | Components with inductive parts                                                             | E48-20a Fault current Teil 1, Teil 2                         |  |

| E-21 Backfeeds                                           | Components that are electrically connected to T.15 or other terminals with wake-up function | E48-21 Short circuit in signal circuit and load circuits     |  |

| E-22 Overcurrents                                        | Components that have an output                                                              |                                                              |  |

|                                                          | ·                                                                                           |                                                              |  |

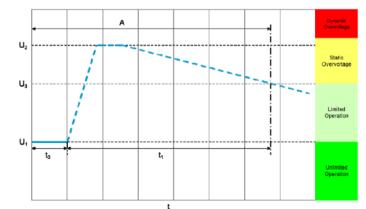

### E01 Long-term overvoltages

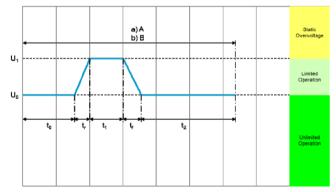

### E48-01a Long-term overvoltages

Aim: The component's resistance to long-term overvoltage is tested. A generator control fault during driving operation is simulated.

| DUT operating mode | Operating mode II.c     |

|--------------------|-------------------------|

| V <sub>max</sub>   | 17 V (+4%, 0%)          |

| V <sub>min</sub>   | 13,5 V                  |

| t,                 | <10 ms                  |

| t <sub>f</sub>     | <10 ms                  |

| t <sub>1</sub>     | 60 min                  |

| Ttest              | T <sub>max</sub> – 20 K |

| Number of cycles   | 1                       |

| Number of DUTs     | At least 6              |

#### **Requirements**:

Components necessary for driving operation: Functional status B For all other components: Functional status C

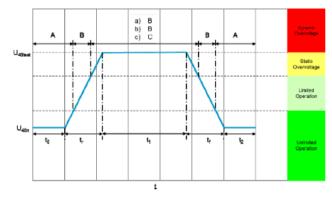

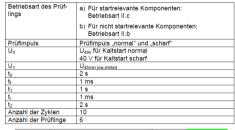

| Betriebsart des Prüflings | Betriebsart II.a, II.b und II.c |

|---------------------------|---------------------------------|

| to                        | Funktionszustand A eingenommen  |

| tr                        | 0,1 s                           |

| t <sub>1</sub>            | 60 min                          |

| t <sub>f</sub>            | 0,1 s                           |

| t <sub>2</sub>            | 1s                              |

| U <sub>48test</sub>       | U <sub>48r,dyn</sub>            |

| T <sub>test</sub>         | T <sub>max</sub> - 20 °C        |

| Anzahl der Zyklen         | 1                               |

| Anzahl der Prüflinge      | 6                               |

#### Requirements:

Components which convert electrical energy: Functional status B Components necessary for driving operation: Functional status B For all other components: Functional status C

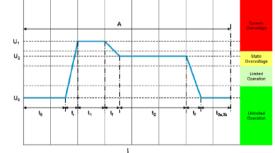

### E48-01b Long-term overvoltages on recuperating components

Aim: Testing for recuperation components in the electrical system where the energy can not be removed and therefore it results in a over voltage.

**Part 1** Test with a source which does not act as a sink. Regenerative current < 10 mA. Current measurement must be made.

| Betriebsart des Prüflings | Betriebsart II.c                                        |

|---------------------------|---------------------------------------------------------|

| T <sub>test</sub>         | T <sub>min</sub> , T <sub>RT</sub> und T <sub>max</sub> |

| U <sub>1</sub>            | U <sub>48max,unlimited</sub>                            |

| U <sub>2</sub>            | U <sub>48r</sub>                                        |

| U <sub>3</sub>            | U <sub>48max,high,limited</sub>                         |

| to                        | ≥ 1 s (die Rückspeisung beginnt nach dieser             |

|                           | Zeit)                                                   |

| t <sub>1</sub>            | ≤ 300 ms                                                |

| Anzahl der Zyklen         | je 3 Zyklen bei allen 3 Temperaturen                    |

| Anzahl der Prüflinge      | 6                                                       |

**Part 2** The DUT is connected to a powerful 4 quadrant amplifier and must be operated for at least t0 at U1. Thereafter, the activation of the feedback begins and at maximum regenerative current of the DUT, the decrease in the regenerative power abruptly (toff) must be terminated.

| Betriebsart des Prüflings | Betriebsart II.c                                        |

|---------------------------|---------------------------------------------------------|

| Ttest                     | T <sub>min</sub> , T <sub>RT</sub> und T <sub>max</sub> |

| U1                        | U48max,unlimited                                        |

| U <sub>2</sub>            | U <sub>48r</sub>                                        |

| U <sub>3</sub>            | U <sub>48max,high,limited</sub>                         |

| to                        | ≥1s                                                     |

| t <sub>1</sub>            | ≤ 300 ms                                                |

| t <sub>off</sub>          | ≤ 10 µs                                                 |

| Anzahl der Zyklen         | je 3 Zyklen bei allen 3 Temperaturen                    |

| Anzahl der Prüflinge      | 6                                                       |

**Requirements**: Functional status A.

The time t1 from the voltage exceeding U1 until voltage falls below U3 must not be exceeded and must be determined!

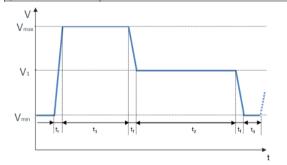

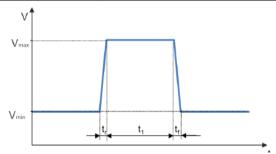

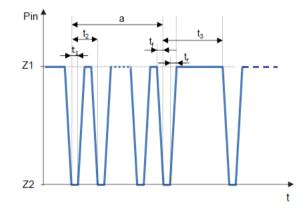

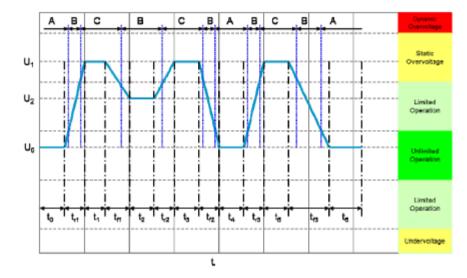

### E02 Transient overvoltages

### E48-02 Transient overvoltages

Aim: Transient overvoltages may occur in the electric system due to the switching off of loads and due to short accelerator tip-ins. These overvoltages are simulated by means of this test.

| DUT operating mode | Operating mode II.c |  |

|--------------------|---------------------|--|

| V <sub>min</sub>   | 16 V                |  |

| U <sub>1</sub>     | 17 V                |  |

| V <sub>max</sub>   | 18 V (+4%, 0%)      |  |

| t,                 | 1 ms                |  |

| tr                 | 1 ms                |  |

| t1                 | 400 ms              |  |

| t <sub>2</sub>     | 600 ms              |  |

| Number of DUTs     | At least 6          |  |

| Test case 1        |                     |  |

| T <sub>test</sub>  | T <sub>max</sub>    |  |

| Number of cycles   | 3                   |  |

| t3                 | 2 s                 |  |

| Test case 2        |                     |  |

| T <sub>test</sub>  | T <sub>min</sub>    |  |

| Number of cycles   | 3                   |  |

| t <sub>3</sub>     | 2 s                 |  |

| Test case 3        |                     |  |

| T <sub>test</sub>  | T <sub>RT</sub>     |  |

| Number of cycles   | 100                 |  |

| t3                 | 8 s                 |  |

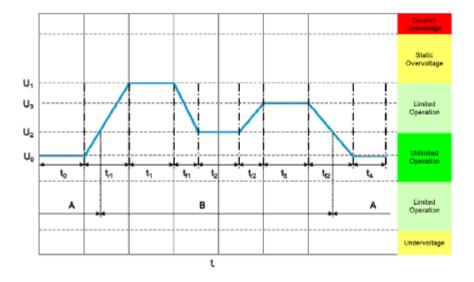

| Betriebsart des Prüflings | Betriebsart II.c                                       |

|---------------------------|--------------------------------------------------------|

| Uo                        | U <sub>48n</sub>                                       |

| U <sub>1</sub>            | 70 V                                                   |

| U <sub>2</sub>            | U <sub>48r</sub>                                       |

| to                        | 100 ms                                                 |

| tr                        | 1 ms                                                   |

| t <sub>1</sub>            | 40 ms                                                  |

| tr                        | 1 ms                                                   |

| t <sub>2</sub>            | 600 ms                                                 |

| t <sub>3a</sub>           | 2,5 s                                                  |

| t <sub>3b</sub>           | 9 s                                                    |

| R <sub>i</sub>            | $10 \text{ m}\Omega \le R_i \le 100 \text{ m}\Omega$   |

| Anzahl der Zyklen         | 1. Kurztest: 3-mal mit t <sub>3a</sub>                 |

|                           | <ol> <li>Dauertest: 1000-mal t<sub>3b</sub></li> </ol> |

|                           | Beide Prüfungen werden sequenziell durchge-<br>führt.  |

| Anzahl der Prüflinge      | 6                                                      |

**Requirements**: Functional status A

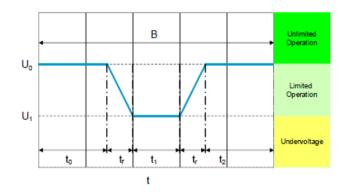

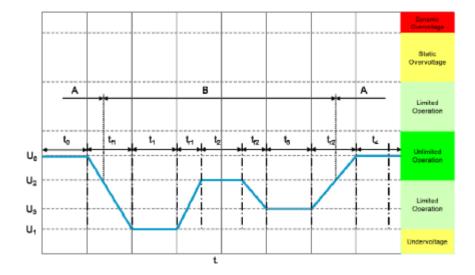

### E-03 Transient undervoltage

### E48-03 Transient undervoltages

Aim: Transient undervoltages in the electric system may occur due to switching on of loads. These undervoltages are simulated by means of this test.

| DUT operating mode | Operating mode II.c |

|--------------------|---------------------|

| V <sub>max</sub>   | 10,8 V (+4%, 0%)    |

| V <sub>min</sub>   | 9 V (0%, −4%)       |

| t                  | 1,8 ms              |

| t <sub>f</sub>     | 1,8 ms              |

| t <sub>1</sub>     | 500 ms              |

| t <sub>2</sub>     | 1s                  |

| Number of DUTs     | At least 6          |

| Test case 1        |                     |

| T <sub>test</sub>  | T <sub>max</sub>    |

| Number of cycles   | 3                   |

| Test case 2        |                     |

| T <sub>test</sub>  | T <sub>min</sub>    |

| Number of cycles   | 3                   |

**Requirements**: Functional status A

| Betriebsart des Prüf- | Betriebsart II.c               |

|-----------------------|--------------------------------|

| lings                 |                                |

| Uo                    | U <sub>48min,unlimited</sub>   |

| U <sub>1</sub>        | U <sub>48min,low,limited</sub> |

| to                    | 60 s                           |

| t <sub>f</sub>        | 2 ms                           |

| t <sub>1</sub>        | 500 ms                         |

| t,                    | 2 ms                           |

| t <sub>2</sub>        | 500 ms                         |

| Anzahl der Zyklen     | 1                              |

| Anzahl der Prüflinge  | 6                              |

**Requirements**: Functional status B

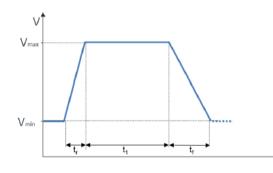

### E-04 Jumpstart

### E48-04 Jumpstart / recuperation

Aim: Jump starting of the vehicle is simulated. The maximum test voltage results from commercial vehicle systems and their elevated electric system voltages.

| DUT operating mode | Operating mode II.c |

|--------------------|---------------------|

| V <sub>min</sub>   | 10,8 V              |

| V <sub>max</sub>   | 26 V (+4%, 0%)      |

| t <sub>1</sub>     | 60 s                |

| t,                 | <10 ms              |

| t <sub>r</sub>     | <10 ms              |

| Number of cycles   | 1                   |

| Number of DUTs     | At least 6          |

#### **Requirements**:

Components relevant to starting (e.g., starter): Functional status B Sensors must provide valid values during the entire All other components: Functional status C

www.wks-informatik.de

LV 148: Longer recuperation is simulated.

| Betriebsart des Prüflings | Betriebsart II.c                |

|---------------------------|---------------------------------|

| U <sub>0</sub>            | U <sub>48max,unlimited</sub>    |

| U <sub>1</sub>            | U <sub>48max,high,limited</sub> |

| to                        | 60 s                            |

| t <sub>r</sub>            | 100 ms                          |

| t <sub>1</sub>            | 60 s                            |

| t <sub>f</sub>            | 100 ms                          |

| t <sub>2</sub>            | 60 s                            |

| Anzahl der Zyklen         | 1                               |

| Anzahl der Prüflinge      | 6                               |

#### **Requirements**:

For recuperation and driving relevant components: Functional status A All other components: Functional status B

### E-05 Load dump

Aim: Dumping of an electric load, in combination with a battery with reduced buffering ability, results in an energy-rich overvoltage pulse due to the generator characteristics. This pulse is simulated by means of this test.

| DUT operating mode   | Operating mode II.c |

|----------------------|---------------------|

| V <sub>min</sub>     | 13,5 V              |

| Vmax                 | 27 V (+4%, 0%)      |

| tr                   | ≤2 ms               |

| t <sub>1</sub>       | 300 ms              |

| t <sub>r</sub>       | ≤30 ms              |

| Break between cycles | 1 min               |

| Number of cycles     | 10                  |

| Number of DUTs       | At least 6          |

#### Requirements:

Safety-relevant components: Functional status B All other components: Functional status C

> WKS Informatik Experts in Testing

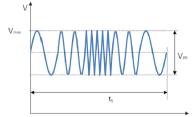

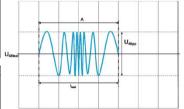

### E-06 Superimposed alternating voltage

### E48-05 Superimposed alternating voltage

Aim: Voltages may be superimposed to the electric system. The superimposed alternating voltage may be applied during the entire running time of the engine.

| DUT operating mode             | Operating mode II.c                                     |

|--------------------------------|---------------------------------------------------------|

| V <sub>max</sub>               | V <sub>Bmax</sub>                                       |

| Ri                             | ≤100 mΩ                                                 |

| Frequency range                | 15 Hz – 30 kHz                                          |

| Wobble duration t <sub>1</sub> | 2 min                                                   |

| Type of wobble                 | Triangle, logarithmic                                   |

| Number of cycles               | 15                                                      |

| Number of DUTs                 | At least 6                                              |

| Test case 1                    |                                                         |

| V <sub>PP</sub>                | 2 V (+4%, 0%)                                           |

| Test case 2                    |                                                         |

| V <sub>PP</sub>                | 3 V (+4%, 0%)                                           |

|                                | only for components between battery and generator,      |

|                                | in particular for battery connection far from generator |

| Test case 3                    |                                                         |

| VPP                            | 6 V (+4%, 0%)                                           |

|                                | for all components during driving without battery       |

|                                | (emergency mode) or for connection close to             |

|                                | generator                                               |

#### **Requirements**:

Test case 1: Functional status A Test case 2: Functional status A Test case 3:

a) Components necessary for driving operation: Functional status A

b) For all other components: Functional status B

www.wks-informatik.de

| Betriebsart II.c                               |

|------------------------------------------------|

| ≤ 60 mΩ                                        |

| Ein hierbei auftretender maximaler Rippelstrom |

| ist mit der Fachabteilung des Auftraggebers    |

| abzustimmen.                                   |

| U <sub>48min.unlimited</sub>                   |

| 30 min                                         |

| F1: 15 Hz bis 30 kHz                           |

| F2: 30 kHz bis 200 kHz                         |

| 2 min                                          |

| Dreieck logarithmisch                          |

| für F1: 6 V ± 2 % (Einzustellen vor Anschluss  |

| an Prüfling)                                   |

| für F2: 2 V ± 2 % (Einzustellen vor Anschluss  |

| an Prüfling)                                   |

| 6                                              |

|                                                |

| Betriebsart des Prüflings | Betriebsart II.c                                                                                                                               |  |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ri                        | ≤ 60 mΩ<br>Ein hierbei auftretender maximaler Rippelstrom<br>ist mit der Fachabteilung des Auftraggebers<br>abzustimmen.                       |  |  |

| U <sub>48test</sub>       | U <sub>48max,unlimited</sub>                                                                                                                   |  |  |

| t <sub>test</sub>         | 30 min                                                                                                                                         |  |  |

| f                         | F1: 15 Hz bis 30 kHz<br>F2: 30 kHz bis 200 kHz                                                                                                 |  |  |

| Wobble-Periode            | 2 min                                                                                                                                          |  |  |

| Wobble-Art                | Dreieck logarithmisch                                                                                                                          |  |  |

| U <sub>48pp</sub> ,       | für F1: $6 \vee \pm 2 \%$ (Einzustellen vor Anschluss<br>an Prüfling)<br>für F2: $2 \vee \pm 2 \%$ (Einzustellen vor Anschluss<br>an Prüfling) |  |  |

| Anzahl der Prüflinge      | 6                                                                                                                                              |  |  |

**Requirements**:

All components: Functional status A

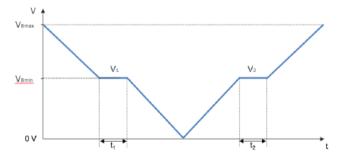

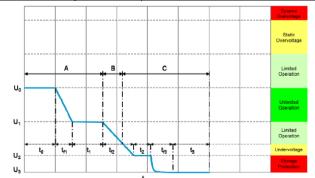

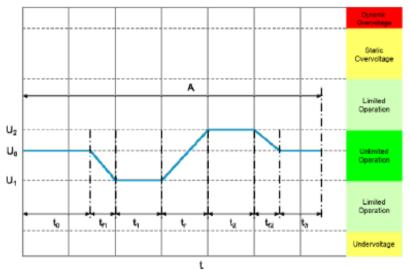

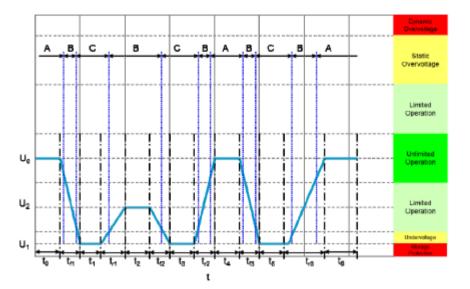

### E-07 Slow decrease and increase of the supply voltage

# E48-06a Slow decrease and increase of the supply voltage (without energy storage )

Aim: The slow decrease and increase of the supply voltage is simulated as it occurs during the slow descharging and charging procedure of the vehicle battery.

| DUT operating mode   | Operating mode II.a and II.c                                                                                                    |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                      | Must be performed for all relevant statuses of the voltage supply terminals (e.g., T.15, T.30, T.87) and their combinations.    |

| Start voltage        | V <sub>Bmax</sub> (+4%, 0%)                                                                                                     |

| Voltage change speed | 0,5 V/min (+10%, -10%)                                                                                                          |

| U <sub>1</sub>       | V <sub>Bmin</sub>                                                                                                               |

| t <sub>1</sub>       | Holding time at V <sub>1</sub> until event memory has been<br>completely read out                                               |

| Minimum voltage      | 0 V                                                                                                                             |

| U <sub>2</sub>       | V <sub>Bmin</sub>                                                                                                               |

| t2                   | Holding time at V <sub>2</sub> until event memory has been<br>completely read out                                               |

| Final voltage        | V <sub>Bmax</sub> (+4%, 0%)                                                                                                     |

| Number of cycles     | Per relevant terminal status and their<br>combinations:<br>1 cycle with operating mode II.a<br>1 cycle with operating mode II.c |

| Number of DUTs       | At least 6                                                                                                                      |

#### **Requirements**:

Within the defined operating voltage of the component: Functional status A Outside of the defined operating voltage of the component: Functional status C

| Betriebsart des Prüflings | Betriebsart II.a und II.c              |  |

|---------------------------|----------------------------------------|--|

| U <sub>0</sub>            | U <sub>48max,unlimited</sub>           |  |

| Spannungsgradient         | ± 2 V/min                              |  |

| U <sub>1</sub>            | U <sub>48min,unlimited</sub>           |  |

| U <sub>2</sub>            | 0 V                                    |  |

| t1                        | Solange bis Fehlerspeicher vollständig |  |

| 11                        | ausgelesen wurde                       |  |

| Anzahl der Zyklen         | 1 Zyklus in Betriebsart II.a           |  |

|                           | 1 Zyklus in Betriebsart II.c           |  |

| Anzahl der Prüflinge      | 6                                      |  |

**Requirements**: depends on voltage range

# E48-06b Slow decrease and increase of the supply voltage (with energy storage – Part 1 )

**Aim:** Checks will slow the supply voltage decrease to the energy storage protection voltage, followed by energy storage disconnection.

| Betriebsart des Prüflings | Betriebsart II.a                      |

|---------------------------|---------------------------------------|

| U <sub>0</sub>            | U <sub>48max,unlimited</sub>          |

| U <sub>1</sub>            | U <sub>48min,unlimited</sub>          |

| U <sub>2</sub>            | U <sub>48stoprotect</sub>             |

| U <sub>3</sub>            | 0 V                                   |

| to                        | 100 ms                                |

| t <sub>f1</sub>           | 8 min                                 |

| +                         | ≥ 60 s (während dieser Phase wird der |

| t <sub>1</sub>            | Fehlerspeicher ausgelesen)            |

| t <sub>f2</sub>           | 8 min                                 |

| t <sub>2</sub>            | 60 s                                  |

| t <sub>r3</sub>           | 3 s                                   |

| t <sub>3</sub>            | 60 s                                  |

| Anzahl der Zyklen         | 1                                     |

| Anzahl der Prüflinge      | 6                                     |

Requirements: depends on voltage range www.wks-informatik.de

# E48-06c Slow decrease and increase of the supply voltage (with energy storage – Part 2)

**Aim:** Checks the behavior that occurrs when the electrical system is operated without battery, and then a discharged battery is connected

| Betriebsart des Prüflings | Betriebsart II.b nach Erreichen der End- |  |  |

|---------------------------|------------------------------------------|--|--|

| -                         | spannung                                 |  |  |

| Ri                        | ≤ 60 mΩ                                  |  |  |

| U <sub>0</sub>            | 0 V                                      |  |  |

| U <sub>1</sub>            | U <sub>48n</sub>                         |  |  |

| U <sub>48pp</sub>         | 6 V bei 10 kHz                           |  |  |

| U <sub>2</sub>            | U <sub>48stoprotect</sub>                |  |  |

| t <sub>0</sub>            | 100 ms                                   |  |  |

| t <sub>r1</sub>           | 300 ms                                   |  |  |

| t1                        | ≥ 60 s (während dieser Phase wird der    |  |  |

| 4                         | Fehlerspeicher ausgelesen)               |  |  |

| t <sub>r1</sub>           | 1 ms                                     |  |  |

| t <sub>r2</sub>           | 14 min                                   |  |  |

| t <sub>3</sub>            | 100 ms                                   |  |  |

| Anzahl der Zyklen         | 1                                        |  |  |

| Anzahl der Prüflinge      | 6                                        |  |  |

**Requirements**: depends on voltage range

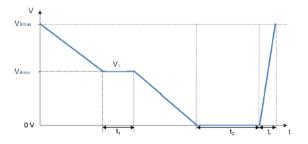

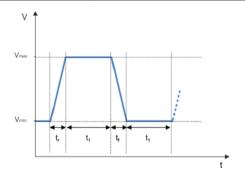

### E08 Slow decrease, quick increase of the supply voltage

**Aim:** This test simulates the slow decrease of the battery voltage to 0 V and the sudden reapplication of the battery voltage, e.g., by applying a jump start source.

| DUT operating mode                | Operating mode II.a and II.c                               |  |  |  |  |

|-----------------------------------|------------------------------------------------------------|--|--|--|--|

| 1 3                               |                                                            |  |  |  |  |

|                                   | Must be performed for all relevant statuses of the voltage |  |  |  |  |

|                                   | supply terminals (e.g., T.15, T.30, T.87) and their        |  |  |  |  |

|                                   | combinations.                                              |  |  |  |  |

| Start voltage                     | V <sub>Bmax</sub> (+4%, 0%)                                |  |  |  |  |

| Voltage drop                      | 0,5 V/min (+10%, -10%)                                     |  |  |  |  |

| V <sub>1</sub>                    | V <sub>Bmin</sub>                                          |  |  |  |  |

| t,                                | Holding time at V <sub>1</sub> until event memory has been |  |  |  |  |

| ч                                 | completely read out                                        |  |  |  |  |

| Holding time at V <sub>Bmin</sub> | Until the event memory is completely read out.             |  |  |  |  |

| Minimum voltage                   | 0 V                                                        |  |  |  |  |

| ta                                | At least 1 min; however, as long as internal capacity is   |  |  |  |  |

| -                                 | completely discharged                                      |  |  |  |  |

| Final voltage                     | V <sub>Bmax</sub> (+4%, 0%)                                |  |  |  |  |

| tr                                | ≤0,5 s                                                     |  |  |  |  |

| Number of cycles                  | Per relevant terminal status and their combinations:       |  |  |  |  |

|                                   | 1 cycle with operating mode II.a                           |  |  |  |  |

|                                   | 1 cycle with operating mode II.c                           |  |  |  |  |

| Number of DUTs                    | At least 6                                                 |  |  |  |  |

#### **Requirements**:

Within the defined operating voltage of the component: Functional status A Outside of the defined operating voltage of the component: Functional status C

### E48-07 Slow decrease, fast increase in the supply voltage

**Aim:** This test simulates the slow decrease of the vehicle system voltage to the energy storage protection voltage followed by shutdown to 0V and the sudden reconnect the system voltage by a charged or new energy storage battery.

| Betriebsart des Prüflings | Betriebsart II.a                      |  |  |  |

|---------------------------|---------------------------------------|--|--|--|

| Uo                        | U <sub>48max,unlimited</sub>          |  |  |  |

| U <sub>1</sub>            | U <sub>48min,unlimited</sub>          |  |  |  |

| U <sub>2</sub>            | U <sub>48stoprotect</sub>             |  |  |  |

| U <sub>3</sub>            | 0 V                                   |  |  |  |

| U <sub>4</sub>            | U <sub>48n</sub>                      |  |  |  |

| to                        | 100 ms                                |  |  |  |

| tn                        | 8 min                                 |  |  |  |

| •                         | ≥ 60 s (während dieser Phase wird der |  |  |  |

| t <sub>1</sub>            | Fehlerspeicher ausgelesen)            |  |  |  |

| t <sub>f2</sub>           | 8 min                                 |  |  |  |

| t <sub>2</sub>            | 60 s                                  |  |  |  |

| t <sub>f3</sub>           | 3 s                                   |  |  |  |

| t <sub>3</sub>            | 300 s                                 |  |  |  |

| t <sub>r1</sub>           | ≤ 100 ms                              |  |  |  |

| t <sub>4</sub>            | 100 ms                                |  |  |  |

| Anzahl der Zyklen         | 1                                     |  |  |  |

| Anzahl der Prüflinge      | 6                                     |  |  |  |

WKS

Informatik Experts in Testing

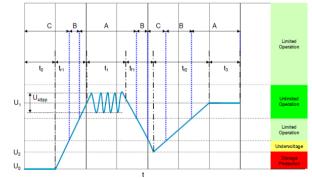

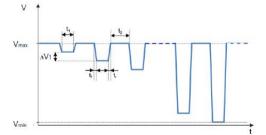

### E09 Reset behavior

### E48-08 Reset behavior

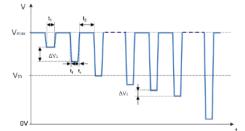

**Aim:** The reset behavior of a component in its environment is simulated and tested. Test boundary conditions (e.g., assembly, terminal, system) must be described in detail. During operation, an arbitrary sequence of repeated switching-on/off procedures occurs; this must not lead to an undefined behavior of the component. The reset behavior is represented by a voltage variance and a time variance. Two different test sequences are required to simulate different switch-off times. A component must always undergo both sequences.

| DUT operating mode                                                | Operating mode II.a and II.c                          |  |  |

|-------------------------------------------------------------------|-------------------------------------------------------|--|--|

|                                                                   | Must be performed for all relevant statuses of the    |  |  |

|                                                                   | voltage supply terminals (e.g., T.15, T.30, T.87) and |  |  |

|                                                                   | their combinations.                                   |  |  |

| V <sub>max</sub>                                                  | V <sub>Bmin</sub> (0%, -4%)                           |  |  |

| Vth                                                               | 6 V                                                   |  |  |

| ΔV <sub>1</sub> (range from V <sub>max</sub> to V <sub>th</sub> ) | 0,5 V                                                 |  |  |

| $\Delta V_2$ (range from V <sub>th</sub> to 0 V)                  | 0,2 V                                                 |  |  |

| t <sub>2</sub>                                                    | At least ≥10 s and until the DUT has returned to 100% |  |  |

|                                                                   | operability (all systems rebooted without error).     |  |  |

| tr                                                                | ≤10 ms                                                |  |  |

| t <sub>r</sub>                                                    | ≤10 ms                                                |  |  |

|                                                                   | For each test sequence, per relevant terminal status  |  |  |

|                                                                   | and their combinations:                               |  |  |

|                                                                   | 1 cycle with operating mode II.a                      |  |  |

| Number of cycles                                                  | 1 cycle with operating mode II.c                      |  |  |

| Number of DUTs                                                    | At least 6                                            |  |  |

| Test case 1                                                       |                                                       |  |  |

| t <sub>1</sub>                                                    | 5s                                                    |  |  |

| Test case 2                                                       |                                                       |  |  |

| t <sub>1</sub>                                                    | 100 ms                                                |  |  |

|                                                                   | *                                                     |  |  |

#### Requirements:

Functional status A when Vmax is reached again.Undefined operating statuses must not occur under any circumstances. It must be verified and documented that the specified threshold voltage level beyond which the component leaves functional status A for the first time is adhered to.

#### www.wks-informatik.de

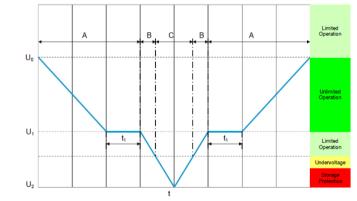

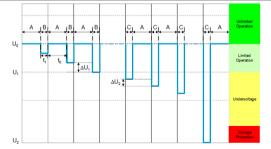

| Betriebsart des Prüflings                                     | Betriebsart II.c                                                                                                                                     |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| U <sub>0</sub>                                                | U <sub>48min,unlimited</sub>                                                                                                                         |

| $\Delta U_1$ (Bereich zwischen $U_0$ bis $U_1$                | 2 V                                                                                                                                                  |

| U <sub>1</sub>                                                | U <sub>48min,low,limited</sub>                                                                                                                       |

| ∆U <sub>2</sub> (Bereich U <sub>48min,low,limited</sub> bis 0 |                                                                                                                                                      |

| V)                                                            | 0,5 ∨                                                                                                                                                |

| U <sub>2</sub>                                                | 0 V                                                                                                                                                  |

| to                                                            | mindestens 10 s und bis der Prüfling<br>wieder eine 100%-Betriebsfähigkeit er-<br>reicht hat (alle Systeme sind wieder feh-<br>lerfrei hochgefahren) |

| t <sub>1</sub> – Prüfablauf 1                                 | 5 s                                                                                                                                                  |

| t <sub>1</sub> – Prüfablauf 2                                 | 100 ms                                                                                                                                               |

| t <sub>f/r</sub>                                              | ≤ 100 ms (gilt für alle Prüfimpulse)                                                                                                                 |

| Anzahl der Zyklen                                             | 1                                                                                                                                                    |

| Anzahl der Prüflinge                                          | 6                                                                                                                                                    |

#### **Requirements**:

Functional status: A at reaching of U48min, unlimited

**B** up to 24 V, U 48min,low,limited **C** below 24 V U 48 min,low,limited

+ Requirements LV 124

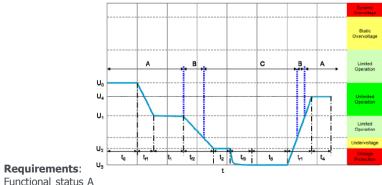

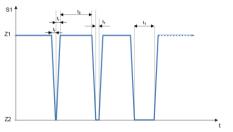

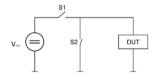

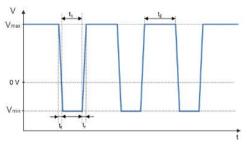

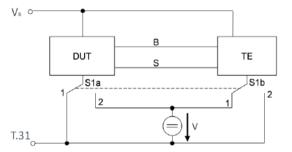

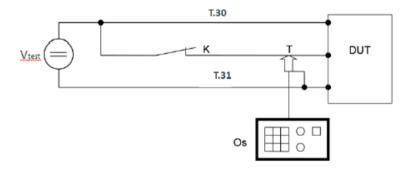

### E10 Short interruptions

E48-09 Short interruptions

Aim: The component's behavior at short interruptions of different durations is simulated.

Test case 1 represents interruption of the supply voltage on the component. Test case 2 represents interruption of the supply voltage in the electric system. Such interruptions can occur due to events such as contact and line errors or bouncing relays.

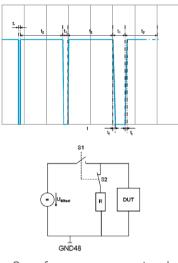

| Operating mode II.c                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 11 V                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| S1 closed                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| S1 open                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| ≤(0,1 * t <sub>1</sub> )                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| $\leq (0, 1 * t_1)$                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| t <sub>1</sub>                                                 | Intervals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 10 µs to 100 µs                                                | 10 µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |